Depending on the target application, the requirements of the network subsystem also vary considerably. Simple remote control and monitoring applications require only a few thousand bits per second, while high-end storage video applications require continuous gigabit per second throughput.

A major advantage of Xilinx embedded solutions is the flexibility and scalability of their processors, IP cores, and software components.

Any application has a set of basic requirements including price, performance and function. In the process of designing products, appropriate tradeoffs must be made between these basic requirements. In addition, in order to adapt to market conditions in product design and its life cycle, these basic requirements will also change. Therefore, it is very important to use a flexible and extensible platform for product design, because the flexible and extensible platform allows design trade-offs and design modifications without changing the platform or vendor.

In this article, we will discuss some application requirements related to network performance, corresponding design tradeoffs, and some design examples that meet the requirements.

Application requirements

According to the OSI standard, Ethernet belongs to the physical layer interface. Of the various protocol standards used for transmission and network layers, the TCP/IP protocol suite is the most commonly used standard, especially in embedded systems, which has become the de facto standard for network transmission.

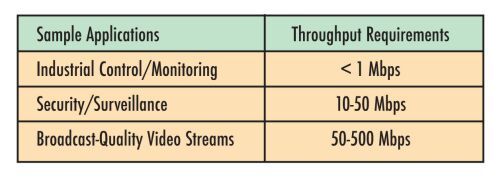

For simplicity, in the remainder of this article, we will use TCP payloads as the primary indicator of performance comparison. Table 1 lists some typical applications and the corresponding TCP/IP payload throughput requirements.

Xilinx Embedded Network Solutions

Xilinx Embedded Solutions gives you all the components and resources you need to build a wide range of embedded network subsystems. One of the major advantages of Xilinx embedded solutions is the flexibility and scalability of their processors, IP cores, and software components. Its powerful flexibility allows you to enable or disable the advanced features of the processor, IP core, and software platform as needed, and fine-tune many of the individual parameters until the application level is met at the software level.

In addition, the use of modeling tools can identify any key performance software function and offload it to the appropriate hardware accelerator.

Let's take a look at three different examples of different Ethernet subsystems. You can use the Xilinx Platform Studio (XPS) to complete the design and meet the performance requirements of such typical applications. Each design has a different system architecture, including processor configuration, Ethernet MAC IP configuration, and memory interface. In addition, these examples highlight different TCP/IP software stacks that can be used in these hardware subsystems. Because the hardware building blocks and software layers are customizable, you can add or remove these sample systems as your application requires.

Table 1: Network throughput requirements for different applications.

Simplify the Ethernet subsystem

For a simple network interface needed for remote monitoring or control applications, minimizing the network subsystem as shown in Figure 1 is sufficient. In such applications, TCP/IP performance requirements are lower (

Using Ethernet Lite IP without interrupts to achieve the design in a simple query mode. At the same time, all software, including simple application layers, can be stored in the local memory in the Xilinx FPGA. For this basic network subsystem, other required I/O interfaces such as RS-232 UART and GPIO can also be added. As shown in Figure 1.

Figure 1. Simplified Ethernet subsystem.

Typical Fast Ethernet (10/100) Subsystem

By making certain modifications to the previous minimum system, a more typical 10/100 and network solution as shown in Figure 2 can be implemented to achieve higher TCP/IP throughput capacity (10-50 Mbit/s). . The main changes are: Add direct memory access (DMA) engine for Ethernet MAC and implement interrupt driver mode; Add external memory to the system, add cache for processor; Use more complex TCP/IP stack, such as Linux (uClinux) System TCP /IP stack.

This MicroBlaze design can be easily created using the basic System Builder wizard in XPS.

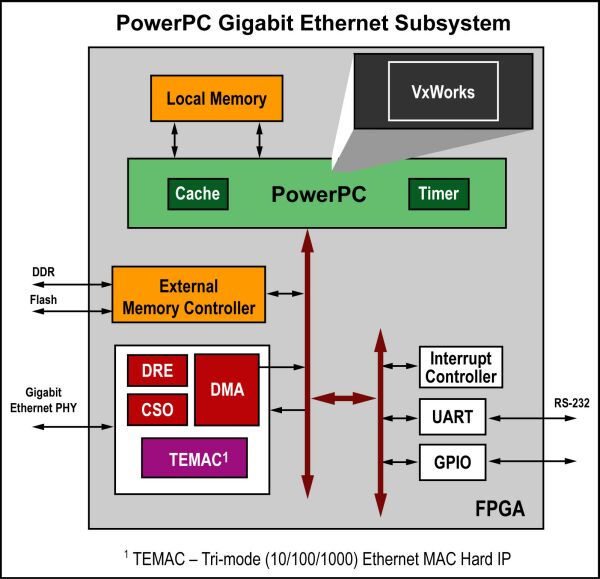

High performance Gigabit Ethernet subsystem

For applications that require 100 Mbit/s and TCP/IP throughput, the built-in three-mode Ethernet MAC hard IP in a dedicated Xilinx FPGA family can be used, as shown in Figure 3. To achieve the required 500+ Mbit/s throughput for high-end applications, it is necessary to use advanced DMA techniques such as scatter/gather DMA (SGDMA) together with data alignment engine (DRE) and checksum shunt (CSO). ) FPGA hardware accelerators.

The high-performance PowerPC 405 implemented on several Xilinx FPGA devices has a built-in 16-Kb instruction and data cache running at 450 MHz to support software platforms such as Linux, VxWorks, Integrity, and QNX, so it can be designed with a high-performance network Interface system.

Figure 2. 10/100 Ethernet.

Figure 3. Gigabit Ethernet.

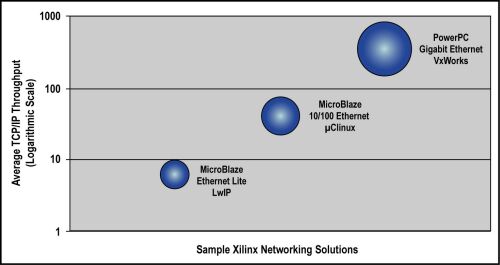

The table in Figure 4 compares TCP/IP payload throughput capabilities for the three network subsystems given earlier. It should be pointed out that since the performance of the three subsystems is very different, the Y axis adopts logarithmic coordinates.

Figure 4. Performance comparison of different Xilinx network solutions.

Factors affecting TCP performance

Many factors affect TCP performance, including hardware and software. The following are related factors that affect the TCP throughput of the system:

Processor

a. Frequency: The TCP/IP protocol usually needs to copy the payload from the user's cache to the buffer controlled by the stack, and then copy it to the Ethernet MAC's FIFO. Some of these memory copy operations are done in software and therefore require processor processing cycles. At the same time, the processor also participates in the calculation of the TCP checksum, and the entire data packet needs to be read out from the memory during the calculation. Faster processors with faster memory can complete these operations in less time, so that higher data rates can be maintained.

b. Function: The TCP/IP stack needs to access the header and payload of the packet. As part of the header processing, typical access includes reading specific bits of header information. Therefore, the processing of each packet requires some shift, addition, and concise operations. In a soft processor such as a configurable MicroBlaze, you must open an instruction to perform a shift or multiplication to get higher performance.

c. Cache: After the packet is copied from the Ethernet MAC to memory, it will pass through different layers of the TCP/IP stack. Then the packet processing code in the TCP/IP stack is executed. Reading all code and data packets into the cache will greatly increase processor efficiency and increase Ethernet bandwidth.

2. Memory: Memory access times and delays have a huge impact on system performance. In a typical application, the TCP/IP stack system is not stored in local memory. Programs and data are stored in external memory. The time it takes to access data and instructions has a large impact on performance. The memory factor is usually related to the size of the cache. Increasing the size of the instruction and data cache helps to reduce the impact of external memory latency and access time.

3. Ethernet MAC: The implementation in the FPGA and network MAC peripherals provide great flexibility, especially in working mode (without DMA and SGDMA), packet FIFO depth, DRE support, CSO support, and jumbo frames ( Jumbo frame) support. Each of these functions affects the resources required by the MAC and how much it can offload from the processor, thus affecting overall performance.

4. TCP/IP Stack: Optimizing the TCP/IP protocol stack flexibly is an important factor affecting system performance. Support for TCP/IP stack functions such as hardware CSO and zero-copy APIs (data does not need to be copied from the application to the stack) and configurable stack options all require system performance support.

5. Message size: The size of the message (application data) is another factor that affects performance. As messages get smaller, the overhead of TCP/IP protocol headers (such as TCP, IP, and Ethernet headers) increases, which reduces overall data payload throughput.

in conclusion

The requirements for network performance in embedded performance vary widely, and these requirements are constantly evolving throughout the product life cycle. In order for the design to meet such a wide and changing range of requirements, flexible and scalable solutions are needed.

Xilinx's embedded solutions, including PowerPC and MicroBlaze processors, comprehensive design tools and customizable IP, help designers build scalable network subsystems that can meet the needs of a wide range of applications .

FDA-APPROVED BLACK BARBECUE GRILL MAT

Yaxing's barbecue grill mats are made from 100% PFOA-Free materials and premium PTFE-Fiberglass coating, no PFOA, silicone or other dangerous chemicals! Certified as safe by the FDA approved! Make your meal healthier when cooking on your BBQ grill with our professional grade.

Yaxing's grill sheets are approved by the FDA and are safe for use on the top shelf of dishwasher.

Its non stick performance makes sure that nothing will stick to this grill mat. What's the most important thing is that Yaxing's grill sheets are durable and reusable.

BBQ Grill Mat,Non Stick Baking Liner,Cooking Grill Mat ,PTFE Grill Sheet

TAIZHOU YAXING PLASTIC INDUSTRY CO., LTD , https://www.yaxingptfe.com