Abstract: Multi-core processors have become the mainstream of processors and developed into mainstream processing platforms for various communications and media applications. The communication structure is one of the core technologies in the multi-core system, and the efficiency of inter-core communication is an important index that affects the performance of the multi-core processor. There are currently three main communication architectures: bus system structure, crossbar network and on-chip network. The bus structure design is relatively convenient, the hardware consumption is less, and the cost is lower; the crossbar switch is a switching network structure suitable for building large-capacity systems; and the on-chip network is a higher-level, larger-scale network system on chip, which can currently solve multi-core The architecture problem is one of the most promising solutions for multi-core systems. While analyzing the basic principle, system structure and function of NoC structure, the article also provides the design and implementation of some units.

Keywords: multi-core processor; inter-core communication; bus structure; crossbar switch; on-chip network

In the development of processors, it is more and more difficult to increase the processor's main frequency. It is difficult to see the traditional single processor with a chip main frequency higher than 4 CHz on the market. Represented by Intel and AMD, the era of relying on continuously increasing processor frequency to improve system performance is about to become a thing of the past. There are three reasons for this: first, it is difficult to significantly improve the performance of the CPU by simply increasing the main frequency, thereby slowing consumers' enthusiasm for high-frequency CPUs; second, when the main frequency of the CPU reaches above 2 GHz, the processor power consumption also Nearly 100 W, which is the limit of current air-cooled heat dissipation technology; third, in the field of embedded products, the traditional single-core processor structure cannot meet the requirements of a geometrically increasing computing scale. In the single-core mode, the development of using local performance to improve the overall performance is slower and slower, while the multi-core-based thread-level parallel technology provides the power for performance improvement. In order to achieve higher processing efficiency, the multi-core processor architecture came into being. .

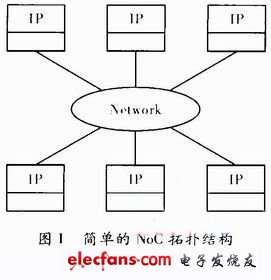

A multi-core processor is a chip that contains two or more "execution cores". Multi-core processors are facing more challenges than single-core processors in the technical research of architecture, such as inter-core communication, memory system, low power consumption, software and hardware coordination, etc. How to achieve mutual cooperation and communication between multi-core cores to ensure increased processing speed and chip processor performance is the main content of inter-core communication structure research. In the multi-core communication method, except for the bus structure in single-core SoC, such as AMBA, CoreConnect, Wishbone, OCP, C * BUS, etc., there are mainly crossbar switches (Crossbar Switch), network on chip (NoC, Network on-Chip ) And other structures. Among them, the NoC structure is a higher-level and larger-scale network system on a chip, which can currently solve the problem of multi-core architecture and is one of the effective solutions for multi-core systems.

1 Problems solved by NoC and their advantages

With the advancement of technology, the limitations of product performance, area, power consumption and time to market have made the design and development requirements higher and higher. The problems caused by the deep submicron design make it more difficult to ensure timing closure in the design. The emergence of NoC (Network on-Chip) has brought continuous development momentum to deep submicron SoCs. NoC is a higher-level, larger-scale system-on-a-chip, a network system on a chip. The core idea of ​​NoC technology is to transplant computer network technology into chip design to solve the problem of multi-CPU architecture. Since the network structure is essentially a multi-CPU system, the network-based architecture is one of the most promising solutions for multi-CPU systems. The on-chip network inherits the concepts of distributed systems and computer networks. The interconnection structure has parallel communication between communication modules. The data has high communication bandwidth, good scalability, and large throughput. It can improve deep / super deep to a certain extent. The advantages of signal transmission line delay under sub-micron conditions, some people say that NoC will become the mainstream interconnect structure of the next generation of multi-core.

1.1 Problems solved by NoC

The problems solved by NoC are mainly reflected in the reusability of communication modules and the predictability of communication performance.

(1) Increase the reusability of communication modules. In the general SoC concept, reusability is the reuse of IP modules. The module-based design method can enhance the reusability of the design, thereby reducing the gap between the manufacturing process and the design capability. The advantage of reusable technology is to build the entire system with a module-based design, reduce the design time of developing each component separately, and reduce the possibility of human design errors, thus reducing the design and verification time of the system. However, when the manufacturing process develops below 0.13 μm, the interconnection delay between modules becomes a bottleneck that limits the overall performance of the system. The reuse of IP modules alone is far from meeting the overall performance requirements. The on-chip network structure uses communication components The reusable technology of the company connects the routing connections between different resource units through regular communication components, providing solutions to the problems caused by deep sub-micron technology.

(2) Strengthen the predictability of communication performance. Due to its regular physical layout and communication network structure, the communication performance of the on-chip network becomes predictable. From the perspective of physical performance, the on-chip network structure determines the predictability of the physical performance of its layout. Except for the clock and power supply wiring, the interconnection length and bandwidth between the switching units are the same, and the uncertainty and irregularity of the design are limited within the resource unit, which has no impact on other resource units; from the design From the perspective of verification time, the reusability of the on-chip network based on modules makes the design and verification time predictable. Due to the regularity of the on-chip network structure, design issues such as task allocation are divided into resource units, and the overall application is divided into Independent task. In this way, the design of the on-chip network system is largely independent of the specific implementation stage, and the modularization is better designed, which increases the predictability of communication performance.

1.2 Advantages of NoC

The NoC design uses global asynchronous local synchronization to solve the problem of global synchronization of the entire chip. It has better reusability and scalability, and the average communication bandwidth is higher. In NoC, the communication between the processing core and the network is completed by a simple handshake protocol, so the electrical parameters and clock signals of the network and each processor can be processed relatively independently and are easy to control. In addition, asynchronous communication can be used between the network and the processor, which does not require global synchronization of the system clock, avoiding the clock and area problems caused by the huge clock tree, and the large number of local clock lines can greatly reduce system power consumption.

The NoC synchronization units work together under the premise of observing the communication protocol. If the NoC system needs to be expanded, just add a copy of the existing communication switch in the system, and design a communication interface to integrate the expanded functional unit. It can be completed in NoC's network topology. NoC has a reusable and extensible communication mechanism. At the same time, it uses the Global Asynchronous Local Synchronized (GALS) mode to work without the intervention of global control signals, so NoC has good scalability.

The main indicator of NoC performance is the communication bandwidth. NoC uses global asynchronous local synchronous communication. Although it has obtained some benefits, its disadvantages are also obvious. For example, the real-time communication bandwidth cannot reach the ideal height. However, from the perspective of the average communication bandwidth of the entire NoC, the global average communication bandwidth is higher than the average communication bandwidth based on the bus method. In short, with the gradual improvement of process integration, NoC is superior to traditional design methods in solving global clock synchronization problems, deep sub-micron effects, scalability, and the gap between design and production.

2 Topology of NoC

Topology is concerned with the layout and interconnection of nodes. The choice of NoC topology has a significant impact on system performance and chip area. NoC can adopt different topological structures according to the needs of applications, and can be divided into regular structures and irregular structures. Relative to the regular topology, the irregular topology can improve performance, reduce power consumption, and reduce area, but at the same time produce layout design, uneven line length and other design problems. The measurement standard of the topology is usually based on the theoretical impact on the routing cost and performance. In addition to considering the number of nodes, the number of edges, the network dimension, the network diameter, the average distance, and the halving width in the ordinary network, It is necessary to consider the embedded attributes of the communication mode, such as message throughput, transmission delay, power consumption, and chip product.

Kehei not only sells its products globally but communicates regularly with customers throughout the world insuring that the products continue to meet or exceed expectations. And customer references are available upon request. The shell of LED Downlights adopt integrated design, it optimize efficiency of heat dissipation. PC shade high transmittance ,weather resistance. High cooler rendering index luminous efficiency with soft light output. Low power consumption.Lower heating during operation. Lumen decay: 3 within 1000 hours. Then Lumens be stable.

*Related Products:interior lighting,high efficiency led,down light.

Smd Downlights,5W Smd Downlights,15W Smd Downlights,3W Smd Downlights

SHENZHEN KEHEI LIGHTING TECHNOLOGY CO.LTD , https://www.keheiled.com